Multiplexer

A multiplexer is a combinatorial circuit that is given a certain number (usually a power of two) data inputs, let us say 2n, and n

address inputs used as a binary number to select one of the data inputs. The multiplexer has a single output, which has the same value as the selected data input.

In other words, the multiplexer works like the input selector of a home music system. Only one input is selected at a time, and the selected input is transmitted to the single output. While on the music system, the selection of the input is made manually, the multiplexer chooses its input based on a binary number, the address input.

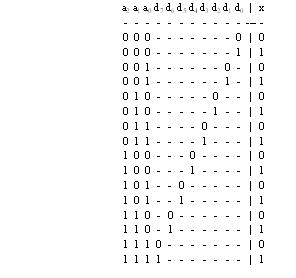

The truth table for a multiplexer is huge for all but the smallest values of n. We therefore use an abbreviated version of the truth table in which some inputs are replaced by `-' to indicate that the input value does not matter.

Here is such an abbreviated truth table for n = 3. The full truth table would have 2(3 + 23) = 2048 rows.

We can abbreviate this table even more by using a letter to indicate the value of the selected input, like this:

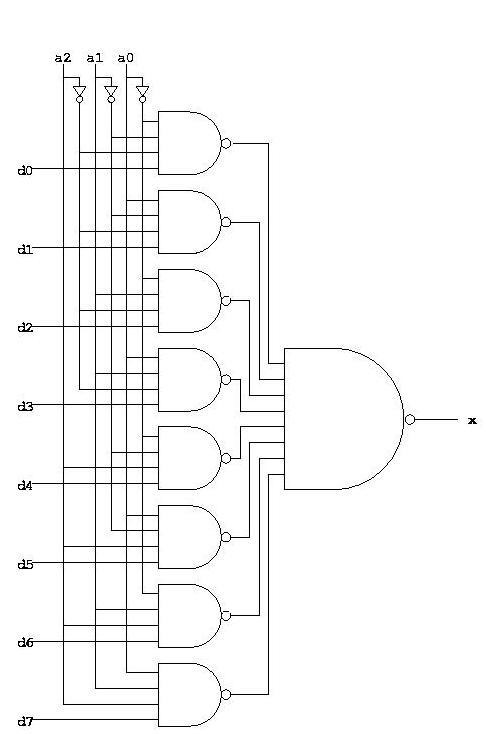

The same way we can simplify the truth table for the multiplexer, we can also simplify the corresponding circuit. Indeed, our simple design method would yield a very large circuit. The simplified circuit looks like this:

Demultiplexer

The demultiplexer is the inverse of the multiplexer, in that it takes a single data input and n address inputs. It has 2n outputs. The address input determine which data output is going to have the same value as the data input. The other data outputs will have the value 0.

Here is an abbreviated truth table for the demultiplexer. We could have given the full table since it has only 16 rows, but we will use the same convention as for the multiplexer where we abbreviated the values of the data inputs.

a2 a1 a0 d | x7 x6 x5 x4 x3 x2 x1 x0

-------------------------------------

0 0 0 c | 0 0 0 0 0 0 0 c

0 0 1 c | 0 0 0 0 0 0 c 0

0 1 0 c | 0 0 0 0 0 c 0 0

0 1 1 c | 0 0 0 0 c 0 0 0

1 0 0 c | 0 0 0 c 0 0 0 0

1 0 1 c | 0 0 c 0 0 0 0 0

1 1 0 c | 0 c 0 0 0 0 0 0

1 1 1 c | c 0 0 0 0 0 0 0

Here is one possible circuit diagram for the demultiplexer:

|